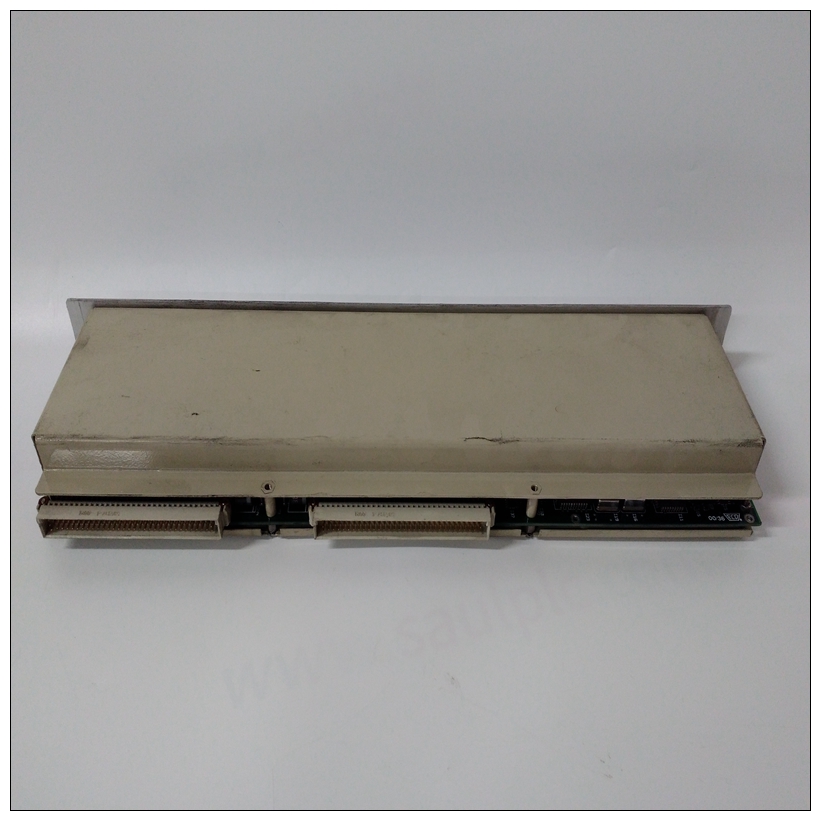

SIOC086406-002自动化卡件,ABB使用配置说明

EPROM/闪存配置头(J20)MVME172LX可以订购2MB闪存和两个EPROM插槽准备好安装EPROM,EPROM位置为标准JEDEC 32引脚DIP支持三种跳线可选密度(256 Kbit x 8;512)的插座Kbit x 8-出厂默认值;1 Mbit x 8),此外还允许禁用闪存接下来的四个表显示了每个EPROM插槽的地址范围四种配置。GPI4(J21引脚9-10)是MC2chip中的控制位ASIC,允许从闪存或EPROM。标题J21提供了八个软件可读跳线。这些跳线可以在MC2chip LCSR中作为寄存器读取(地址为$FFF4202D)。

SIOC086406-002自动化卡件位0与收割台销1-2相关;位7与引脚15-16相关。这个安装跳线时,位值读取为0,安装跳线时,位值读取为1跳线已拆下。MVME172LX出厂时附带如图所示,J21设置为除GPI4之外的所有0(所有引脚上的跳线)在下面如果安装了MVME172BUG固件,则三个跳线可由用户定义(即引脚11-12、13-14、15-16)。如果MVME172BUG固件未安装,七个跳线可由用户定义(即针脚1-2、3-4、5-6、,7-8, 11-12, 13-14, 15-16).注:引脚9-10(GPI4)保留用于选择闪光灯内存映射(已安装跳线)或EPROM内存映射(跳线已拆下)。它们不可由用户定义。地址出现各种EPROM/闪存配置的范围本章的前一节中。MVME172LX出厂时J21设置为全零(所有引脚上的跳线),GPI4除外。内存夹层选项MVME172LX上提供了两个100针连接器(J15和J22)容纳可选内存夹层板。两个内存MVME172LX提供夹层选项:❏ 4、8、16MB奇偶校验DRAM❏ 4、8、16、32、64MB ECC DRAM夹层板可以单独使用,也可以组合使用一堆(不超过两层)。以下连接器选项适用堆叠安排:❏ 4、8和16MB奇偶校验DRAM板在仅底部;它必须是唯一的阁楼或上层阁楼。

❏ 所有ECC DRAM板都有两个连接器选项:–顶部和底部的连接器–仅底部的连接器;必须是唯一的夹层或上层夹层

EPROM/Flash Configuration Header (J20)

The MVME172LX can be ordered with 2MB of Flash memory and two

EPROM sockets ready for the installation of EPROMs, which may be

ordered separately. The EPROM locations are standard JEDEC 32-pin DIP

sockets that support three jumper-selectable densities (256 Kbit x 8; 512

Kbit x 8 — the factory default; 1 Mbit x 8) and which in addition permit

disabling of the Flash memoryThe next four tables show the address range for each EPROM socket in all

four configurations. GPI4 (J21 pins 9-10) is a control bit in the MC2chip

ASIC that allows reset code to be fetched from Flash memory or from

EPROMs.Header J21 provides eight software-readable jumpers. These jumpers can

be read as a register (at address $FFF4202D) in the MC2chip LCSR. Bit 0

is associated with header pins 1-2; bit 7 is associated with pins 15-16. The

bit values are read as a 0 when the jumper is installed, and as a 1 when the

jumper is removed. The MVME172LX is shipped from the factory with

J21 set to all 0s (jumpers on all pins) except for GPI4, as diagrammed

below.If the MVME172BUG firmware is installed, three jumpers are userdefinable (i.e., pins 11-12, 13-14, 15-16). If the MVME172BUG firmware

is not installed, seven jumpers are user-definable (i.e., pins 1-2, 3-4, 5-6,

7-8, 11-12, 13-14, 15-16).

Note Pins 9-10 (GPI4) are reserved to select either the Flash

memory map (jumper installed) or the EPROM memory map

(jumper removed). They are not user-definable. The address

ranges for the various EPROM/Flash configurations appear

in the preceding section of this chapter.

The MVME172LX is shipped from the factory with J21 set to all zeros

(jumpers on all pins) except for GPI4. Memory Mezzanine Options

Two 100-pin connectors (J15 and J22) are provided on the MVME172LX

to accommodate optional memory mezzanine boards. Two memory

mezzanine options are available for the MVME172LX:

❏ 4, 8, 16MB parity DRAM

❏ 4, 8, 16, 32, 64MB ECC DRAM

The mezzanine boards may either be used individually or be combined in

a stack (not more than two deep). The following connector options govern

stacking arrangements:

❏ The 4, 8, and 16MB parity DRAM board has connectors on the

bottom only; it must be either the only mezzanine or the upper

mezzanine.

❏ All ECC DRAM boards are available with two connector options:

– Connectors on both the top and bottom

– Connectors on the bottom only; must be either the only

mezzanine or the upper mezzanine