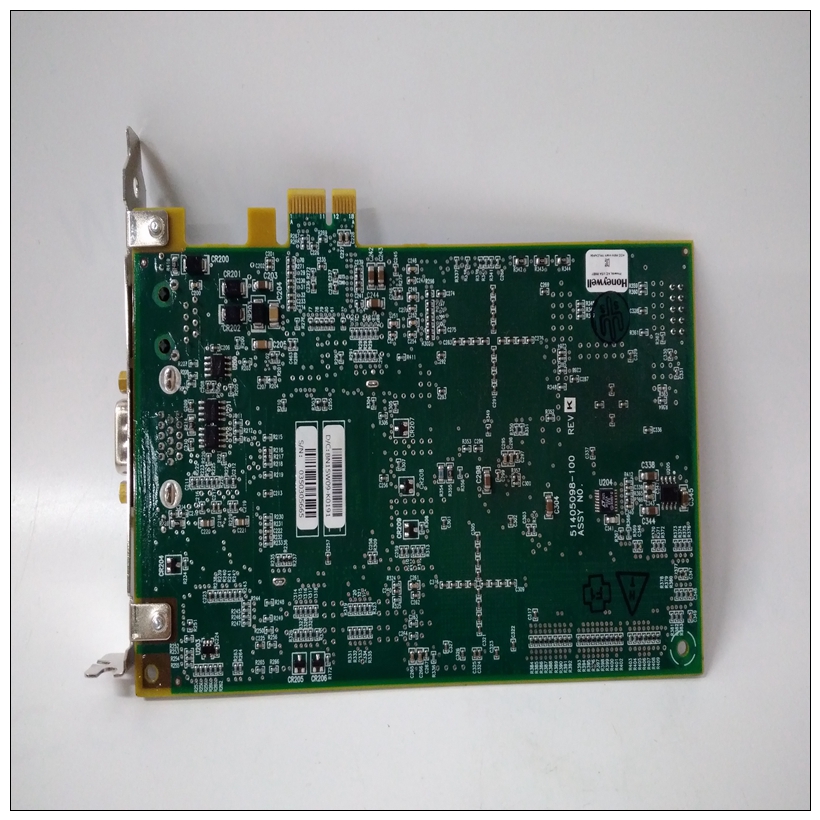

HONEYWELL LCNP4E 51405098-100卡件

本地总线超时每当MPU或PCC出现时,就会发生本地总线超时(LBTO)访问(VMEbus范围外)未在编程时间。如果系统配置正确,则应仅当软件访问车载地址范围。每当LBTO发生时,LBTO状态位在VMEchip中设置。VMEbus访问超时每当PCC或MC68030 VMEbus绑定周期未接收VMEbus总线在编程时间内授予。这通常是由于另一个总线主控器长时间握住总线。当VATO发生时,VATO状态位在VMEchip中设置。

HONEYWELL LCNP4E 51405098-100卡件VMEbus BERR公司*当BERR*信号线激活时,VMEbus BERR*发生当MC68030或PCC是VMEbus主机时。VMEbus BERR*仅在以下情况下发生:❏ 初始化例程采样以查看是否存在设备在VMEbus上,它不是。❏ 坏软件访问VMEbus范围。❏ 错误配置试图访问VMEbus上的设备错误(例如将LWORD*低电平驱动到16位板)。

❏ VMEbus上发生硬件错误。❏ VMEbus从机报告访问错误(例如奇偶校验错误)。

❏ 每当VMEbus BERR*发生时,VMEbus BERR*状态位在VMEchip中设置。

本地RAM奇偶校验错误当启用奇偶校验时,当前总线主机接收到如果正在访问本地总线,则总线错误(或没有LANRDY*,如果LANCE)出现DRAM和奇偶校验错误。如果MC68030是本地总线主机发生奇偶校验错误时,奇偶校验错误(PE)状态位在PCC状态寄存器中设置。注意,该位仅在以下情况下有用:设置模式3奇偶校验。如果设置了模式2奇偶校验,则发生奇偶校验后,MC68030无法读取状态

Local Bus Time-Out

A Local Bus Time-Out (LBTO) occurs whenever an MPU or PCC

access (outside of the VMEbus range) does not complete within the

programmed time. If the system is configured properly, this should

only happen if software accesses a nonexistent location within the

onboard address range. Whenever an LBTO occurs, the LBTO

status bit is set in the VMEchip.

VMEbus Access Time-Out

A VMEbus Access Time-Out (VATO) occurs whenever a PCC or

MC68030 VMEbus bound cycle does not receive a VMEbus Bus

Grant within the programmed time. This is usually caused by

another bus master holding the bus for an excessive period of time.

When a VATO occurs, the VATO status bit is set in the VMEchip.

VMEbus BERR*

The VMEbus BERR* occurs when the BERR* signal line is activated

on the VMEbus while the MC68030 or PCC is the VMEbus master.

VMEbus BERR* should occur only if:

❏ An initialization routine samples to see if a device is present

on the VMEbus and it is not.

❏ Bad software accesses a nonexistent device within the

VMEbus range.

❏ Bad configuration tries to access a device on the VMEbus

incorrectly (such as driving LWORD* low to a 16-bit board).

❏ A hardware error occurs on the VMEbus. ❏ A VMEbus slave reports an access error (such as parity error).

❏ Whenever a VMEbus BERR* occurs, the VMEbus BERR*

status bit is set in the VMEchip.

Local RAM Parity Error

When parity checking is enabled, the current bus master receives a

bus error (or no LANRDY*, if LANCE) if it is accessing the local

DRAM and a parity error occurs. If the MC68030 is the local bus

master when the parity error occurs, the Parity Error (PE) status bit

is set in the PCC status register. Note that this bit is only useful if

mode 3 parity checking is set. If mode 2 parity checking is set, the

MC68030 is not able to read status after the occurrence of the parity

error.