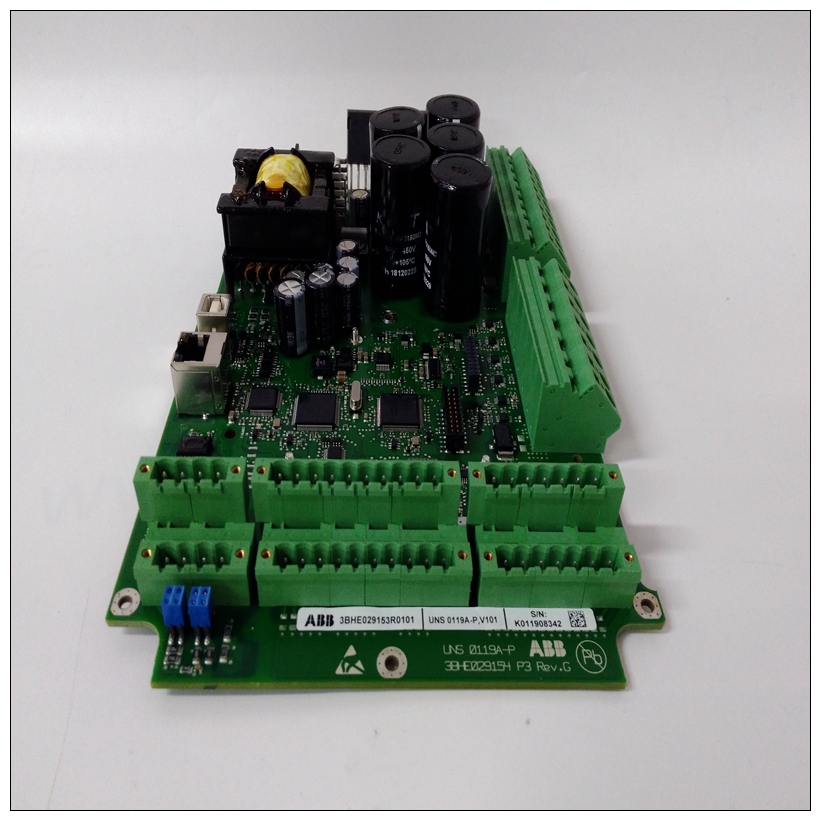

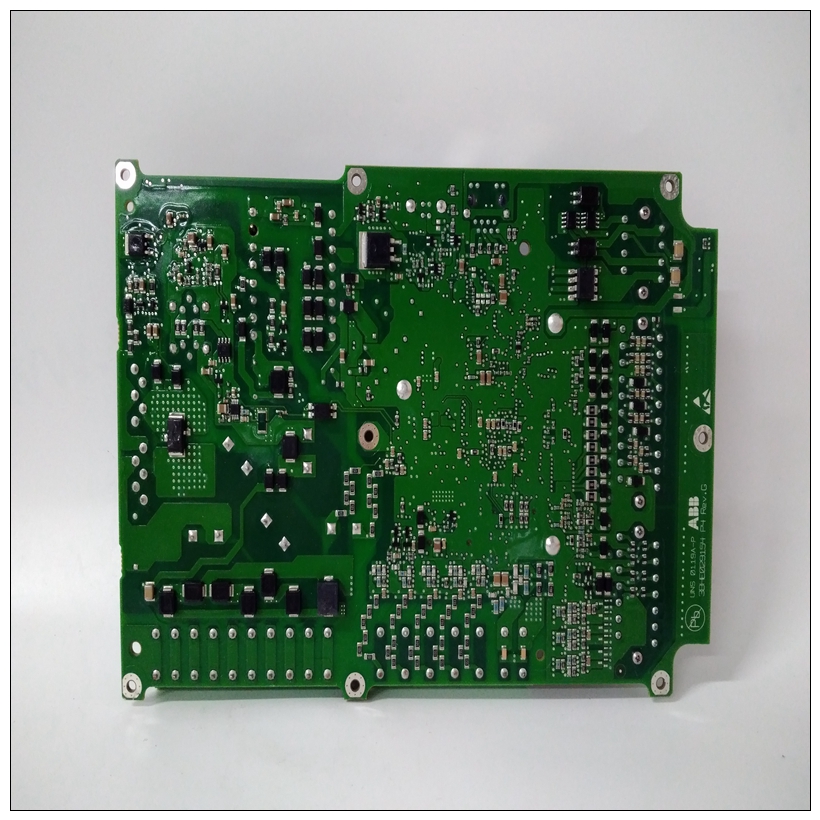

UNS0119A-P,V101 3BHE029153R0101励磁模块,ABB说明书

VMEbus从接口VMEchip为MVME147。当VMEbus想要访问DRAM或VMEchip控制寄存器,VMEbus映射解码器选择VMEchip。对于DRAM访问,VMEchip请求本地总线和获得主控权后,VMEchip激活适当的信号访问DRAM。DRAM通知VMEchip和当DRAM完成时,VMEchip通知VMEbus。访问VMEchip不需要掌握本地总线全局控制和状态寄存器。

UNS0119A-P,V101 3BHE029153R0101励磁模块VMEbus无法访问

MVME147上除DRAM之外的任何其他资源。通用控制芯片(GCC)GCC是一种CMOS ASIC,设计用于取代16个PAL和19个其他PAL先前MVME147单板计算机上的设备。它提供MC68030、VMEchip、PCC、,MVME147上的LANCE和DRAM。同时保留MVME147的原始功能,GCC降低部分和制造成本和降低功耗。

GCC包括以下功能:❏ 本地DRAM控制器:–DRAM阵列的控制信号–MPU到DRAM接口–PCC至DRAM接口–喷管至DRAM接口–VMEchip到DRAM接口–用于MPU和PCC到DRAM的本地总线映射解码器–刷新控制器–字节奇偶校验生成器/检查器

❏ 外部可选内部/外部本地总线仲裁器

❏ MC68030至MC68882接口逻辑

❏ 从奇偶校验和其他错误生成局部总线BERR*

❏ 支持WAITRMC功能

❏ MC68030到VMEbus映射解码器

❏ 其他其他控制逻辑:CIIN*、SCIRST*,异步*SCSI重置因为WD33C93不实现SCSI总线重置(RST),GCC有单独的信号来感应和驱动它。

VMEbus Slave Interface

The VMEchip provides the VMEbus slave interface for the

MVME147. When the VMEbus wants to access the DRAM or

VMEchip control registers, the VMEbus map decoder selects the

VMEchip.

For a DRAM access, the VMEchip requests the local bus and after

obtaining mastership, the VMEchip activates the proper signals to

access the DRAM. The DRAM notifies the VMEchip and the

VMEchip notifies the VMEbus when the DRAM has completed.

Mastership of the local bus is not required to access the VMEchip

Global Control and Status Registers. The VMEbus cannot access

any other resources than DRAM on the MVME147. General Control Chip (GCC)

The GCC is a CMOS ASIC designed to replace 16 PALs and 19 other

devices on the previous MVME147 single board computers. It

provides the interface between the MC68030, VMEchip, PCC,

LANCE, and DRAM on the MVME147. While preserving the

original function of the MVME147, the GCC lowers part and

manufacture cost and reduces power consumption.

The GCC includes the following features:

❏ Local DRAM controller:

– Control signals to DRAM array

– MPU to DRAM interface

– PCC to DRAM interface

– LANCE to DRAM interface

– VMEchip to DRAM interface

– Local bus map decoder for MPU and PCC to DRAM

– Refresh controller

– Byte parity generator/checker

❏ External selectable internal/external local bus arbiter

❏ MC68030 to MC68882 interface logic

❏ Local bus BERR* generation from parity and other errors

❏ Support for WAITRMC function

❏ MC68030 to VMEbus map decoder

❏ Other miscellaneous control logic: CIIN*, SCIRST*,

ASYNCH*

SCSI Reset

Because the WD33C93 does not implement SCSI bus Reset (RST),

the GCC has separate signals to sense and drive it.