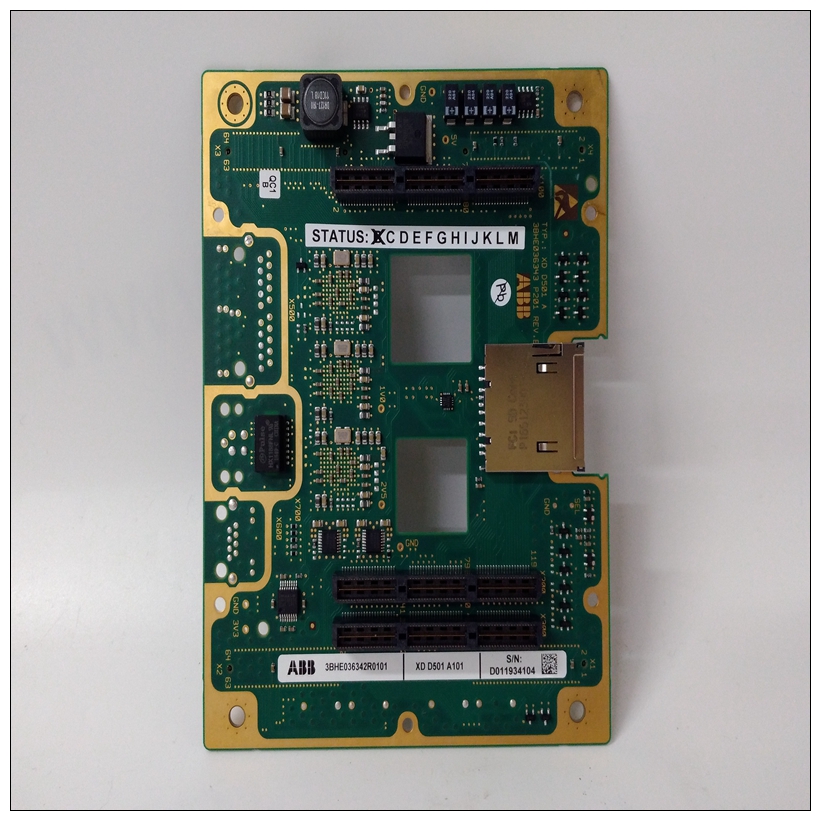

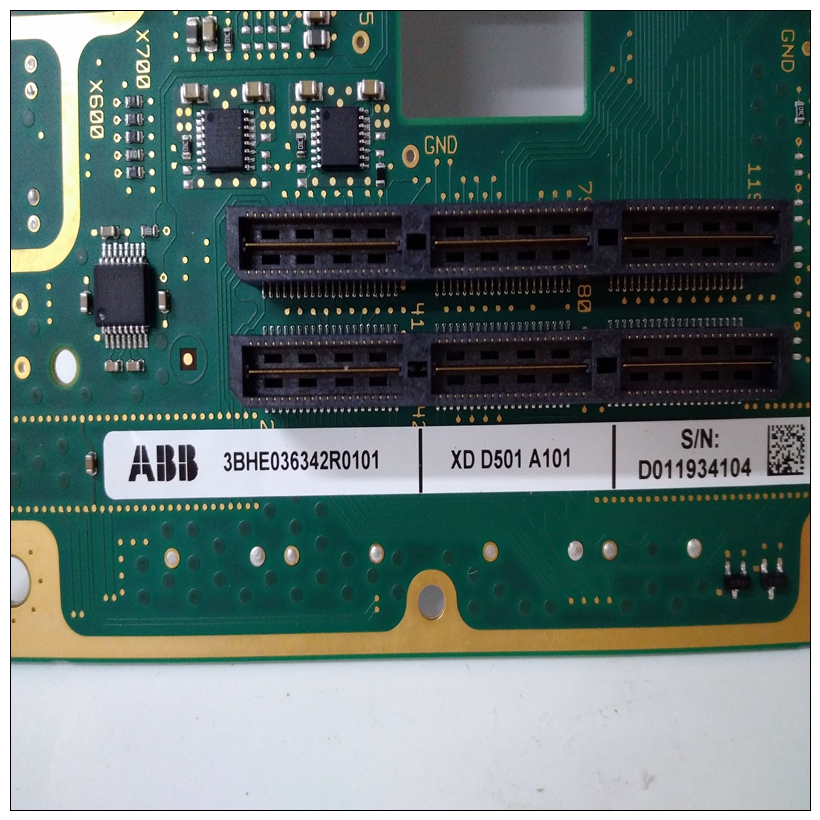

XDD501A101 3BHE036342R0101多通道处理器,ABB英文使用说明

RAM刷新计时器MVME147上使用的DRAM必须至少每15.6µs。GCC至少向DRAM提供刷新信号每15.6µs一次。本地总线多端口仲裁器因为本地地址和数据总线用于访问板载DRAM和VMEbus,任何使用这些设备的设备资源必须首先成为本地总线主节点。MC68030仲裁逻辑(总线请求(BR*)、总线授权(BG*)、总线授权GCC多端口仲裁器使用确认(BGACK*)来将本地总线主控权从当前主控转移到下一个主控主人正常运行期间

XDD501A101 3BHE036342R0101多通道处理器,MC68030为本地总线当PCC、LANCE或VMEbus请求使用本地总线,GCC多端口仲裁器将BR*激活至MC68030。这个MC68030通过激活BG*,完成其当前周期(如果一个正在进行中),并放弃了对当地公交车的控制。此时,GCC多端口仲裁器授予本地总线主控权到最高优先级的请求设备。授予的设备使用然后放弃本地总线主控权。如果另一个设备此时请求本地总线主控,GCC多端口仲裁器将其授予设备;否则,MPU恢复本地总线控制。仲裁优先级从高到低依次为:LANCE、PCC、,VMEbus和MPU。PCC功能重复对PCC中存在的几个寄存器和函数进行了分析GCC中重复。访问这些寄存器和功能是仍然通过PCC地址。然而,PCC上的一些引脚由于逻辑在GCCT内,PCC现在未连接。PCC包括一个DMA通道控制器(DMAC)以移动SCSI芯片和内存之间的数据。DMA信道具有用于数据传输的32位地址指针,32位指针用于命令链接表和24位字节计数器。由于其8位到32位的数据总线宽度转换,该芯片以高达1.5MB/s的速率移动SCSI数据,同时使用少于

对本地进行DMA时,本地总线带宽的25%DRAM。

RAM Refresh Timer

The DRAM used on the MVME147 must be refreshed at least every

15.6 µs. The GCC provides a refresh signal to the DRAM at least

once every 15.6 µs.

Local Bus Multiport Arbiter

Because the local address and data buses are used to access the

onboard DRAM and the VMEbus, any devices that use these

resources must become the local bus master first. The MC68030

arbitration logic (Bus Request (BR*), Bus Grant (BG*), Bus Grant

Acknowledge (BGACK*)) is used by the GCC multiport arbiter to

transfer local bus mastership from the current master to the next

master. During normal operation the MC68030 is the local bus

master.

When the PCC, the LANCE, or the VMEbus requests use of the local

bus, the GCC multiport arbiter activates BR* to the MC68030. The

MC68030 responds by activating BG*, finishing its current cycle (if

one is in progress), and giving up local bus mastership.

At this point, the GCC multiport arbiter grants local bus mastership

to the highest priority requesting device. The granted device uses

the local bus and then relinquishes local bus mastership. If another

device is requesting local bus mastership at this time, the GCC

multiport arbiter grants it to the device; otherwise the MPU

resumes local bus mastership.

The arbitration priority in high to low order is: LANCE, PCC,

VMEbus, and MPU.

Duplication of PCC Functions

Several registers and functions that exist in the PCC have been

duplicated in the GCC. Access to these registers and functions is

still through the PCC addresses. However, some pins on the PCC

are now unconnected because the logic is inside the GCCThe PCC includes a DMA Channel Controller (DMAC) to move

data between the SCSI chip and memory. The DMA channel

features a 32-bit address pointer for data transfers, a 32-bit pointer

for the command chaining table, and a 24-bit byte counter.

Because of its 8-bit to 32-bit data bus width conversion, the chip

moves SCSI data at rates up to 1.5MB/second while using less than

25 percent of the local bus bandwidth when doing a DMA to local

DRAM.