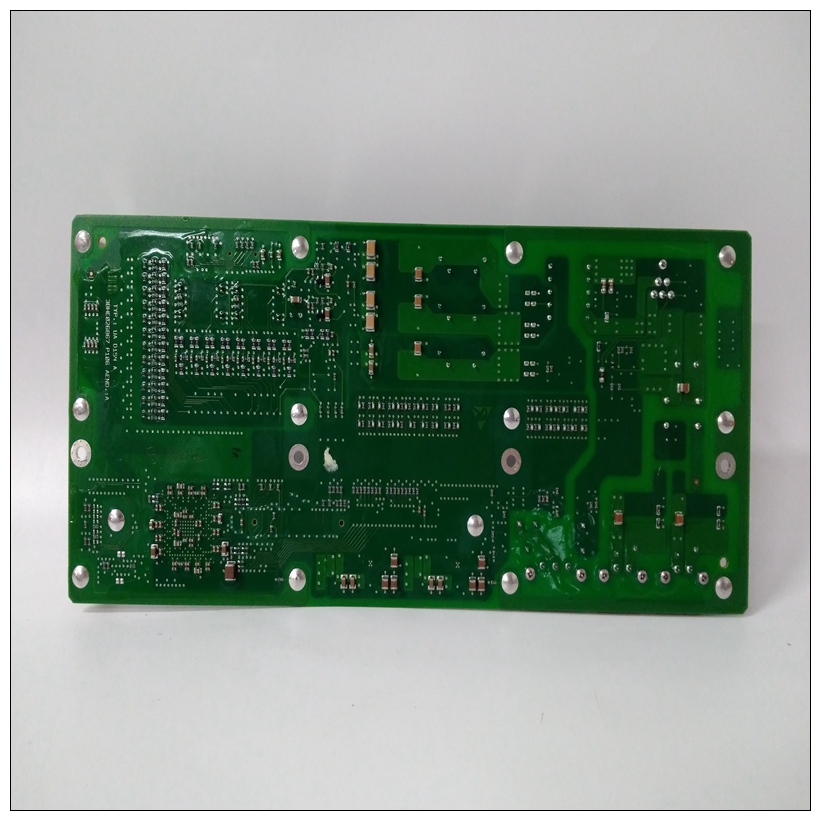

UAD154A 3BHE026866R0101通讯模块,ABB培训教程

位置监视器1配置为监视双字节访问主管短输入/输出地址$00F2,单字节访问短输入/输出地址$00F3。清除后,LM1表示对地址$00F2或$00F3的访问是检测。此时,请求公用事业中断级别4(如果中断已启用)。当中断为已确认或软件向其写入1时。该位设置为1通过SYSRESET。见以下注释。位6位置监视器2配置为监视双字节访问主管短输入/输出地址$00F4,单字节访问短输入/输出地址$00F5。清除后,LM2表示对地址$00F4或$00F5的访问是检测。

UAD154A 3BHE026866R0101通讯模块当软件向其写入1时,设置LM2。此位已设置通过SYSRESET设置为1。见以下注释。位置监视器3配置为监视双字节访问主管短输入/输出地址$00F6,单字节访问短输入/输出地址$00F7。清除后,LM3表示对地址$00F6或$00F7的访问是检测。当软件向其写入1时,设置LM3。此位已设置通过SYSRESET设置为1。见以下注释。GCSR基址配置寄存器必须编程以允许GCSR寄存器组响应VMEbus访问以使此功能启用。执行位置监视器的VMEbus主机循环必须生成DTACK信号以终止周期SIGLP控制信号允许其他VMEbus主机中断MC68030。SIGLP只能从VMEbus。它只能由MC68030清除。当VMEbus主机将SIGLP设置为1,VMEchip请求一个级别1个MC68030中断(如果此类中断已启用)。这个中断请求一直保留,直到MC68030向其写入1。该位由SYSRESET清除。见下文注1。位1 SIGHP控制信号允许其他VMEbus主机中断MC68030。SIGHP只能从VMEbus。它只能由MC68030清除。当VMEbus主机将SIGHP设置为1,VMEchip请求一个级别5中断MC68030(如果此类中断已启用)。这个中断请求一直保留,直到MC68030向其写入1。该位由SYSRESET清除。见下文注1。位4 BRDFAIL是BRDFAIL*输入/输出信号的反射线每当信号线被激活时,状态位被设置为1由VMEchip或看门狗超时激活

来自PCC。

Location monitor 1 is configured to monitor double-byte

accesses to the supervisor short I/O address $00F2, and singlebyte accesses to the short I/O address $00F3. When cleared,

LM1 indicates that an access to address $00F2 or $00F3 was

detected. At such a time, utility interrupt level 4 is requested (if

the interrupt is enabled). LM1 is set when the interrupt is

acknowledged or when software writes a 1 to it. This bit is set to

1 by SYSRESET. See Note below.

Bit 6 Location monitor 2 is configured to monitor double-byte

accesses to the supervisor short I/O address $00F4, and singlebyte accesses to the short I/O address $00F5. When cleared,

LM2 indicates that an access to address $00F4 or $00F5 was

detected. LM2 is set when software writes a 1 to it. This bit is set

to 1 by SYSRESET. See Note below.Location monitor 3 is configured to monitor double-byte

accesses to the supervisor short I/O address $00F6, and singlebyte accesses to the short I/O address $00F7. When cleared,

LM3 indicates that an access to address $00F6 or $00F7 was

detected. LM3 is set when software writes a 1 to it. This bit is set

to 1 by SYSRESET. See Note below.The GCSR Base Address Configuration Register must

be programmed to allow the GCSR set of registers to

respond to VMEbus accesses for this function to be

enabled.

The VMEbus master that executes the location monitor

cycle must generate the DTACK signal to terminate the

cycle. The SIGLP control signal allows other VMEbus masters to

interrupt the MC68030. SIGLP can only be set from the

VMEbus. It can only be cleared by the MC68030. When a

VMEbus master sets SIGLP to a 1, the VMEchip requests a level

1 interrupt to the MC68030 (if such interrupts are enabled). The

interrupt request remains until the MC68030 writes a 1 to it.

This bit is cleared by SYSRESET. See Note 1 below.

Bit 1 The SIGHP control signal allows other VMEbus masters to

interrupt the MC68030. SIGHP can only be set from the

VMEbus. It can only be cleared by the MC68030. When a

VMEbus master sets SIGHP to a 1, the VMEchip requests a level

5 interrupt to the MC68030 (if such interrupts are enabled). The

interrupt request remains until the MC68030 writes a 1 to it.

This bit is cleared by SYSRESET. See Note 1 below.

Bit 4 BRDFAIL is a reflection of the BRDFAIL* input/output signal

line. The status bit is set to 1 whenever the signal line is

activated by either the VMEchip, or by a watchdog time-out