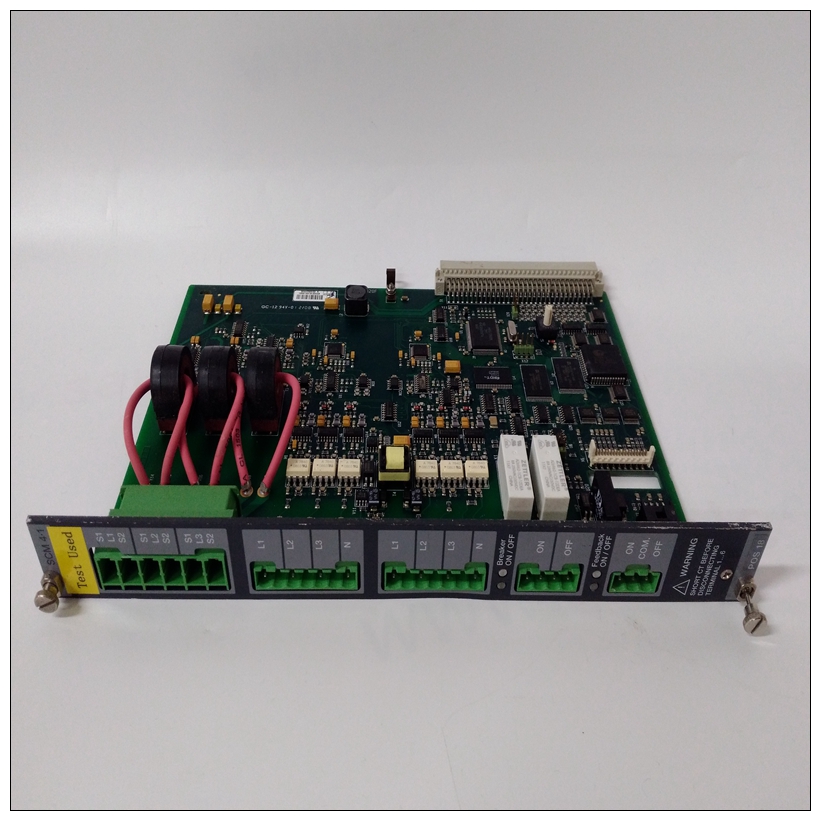

DEIF SCM4.1负载单元控制器,SCM4.1使用配置教程

实用程序中断向量寄存器提供本地每个实用程序都具有唯一向量的CPU中断。仔细检查后发现每个公用电中断的级别,如本章中的实用程序中断掩码寄存器部分是与分配的ID相同。这由反映地址行A01-A03的状态,即当本地CPU确认中断到效用向量寄存器的位0-2。在正常运行过程中访问该寄存器时CPU读取周期,位0-2产生寄存器偏移值(即%xxxxx 001)。

DEIF SCM4.1负载单元控制器实用程序中断向量寄存器的内容当一个公用设施中断时,不得更改处于活动状态。实用程序中断向量寄存器的下三位是由VMEchip编码,以唯一标识导致公用事业中断请求,如表4-7所示。位3-7 UVB3到UVB7是效用向量基位。寄存器的上五位可通过以下方式编程:软件为中提供的矢量提供唯一的基础确认公用电中断之一的过程。这些位通过任何重置清除。该寄存器用于配置中断请求中断器激活以请求中断VMEbus。三条中断电平选择线的编码如所示表4-8。将非0值写入这三个位会导致用于激活相应VMEbus IRQ线路的断路器。由于中断器在确认释放(ROAK)模式下工作,因此中断请求寄存器为清除,当芯片响应VMEbus中断确认周期。这些位通过系统重置。

The utility interrupt vector register provides the local

CPU with a unique vector for each of the utility

interrupts. Close examination reveals that the assigned

level of each of the utility interrupts, as defined in the

Utility Interrupt Mask Register section in this chapter, is

the same as its assigned ID. This is implemented by

reflecting the state of the address lines A01-A03, that

the local CPU drives when it acknowledges an

interrupt, onto bits 0-2 of the utility vector register.

When accessing this register in the course of a normal

CPU read cycle, bit 0-2 yields the register offset value

(which is %xxxxx001).

The contents of the utility interrupt vector register

must not be changed while one of the utility interrupts

is active. The lower three bits of the utility interrupt vector register are

encoded by the VMEchip to uniquely identify the function that

caused the utility interrupt request as shown in Table 4-7.

Bits 3-7 UVB3 through UVB7 are utility vector base bits.

The upper five bits of the register are programmable by

software to provide a unique base for the vector provided in the

course of acknowledging one of the utility interrupts. These bits

are cleared by any reset. This register is used to configure the interrupt request

line that the interrupter activates to request an

interrupt on the VMEbus.

The three interrupt level select lines are encoded as shown in

Table 4-8. Writing a non-0 value to these three bits causes the

interrupter to activate the corresponding VMEbus IRQ line.

Because the interrupter operates in the Release-OnAcknowledge (ROAK) mode, the interrupt request register is

cleared, deactivating the IRQ line when the chip responds to a

VMEbus interrupt acknowledge cycle. These bits are cleared by

SYSRESET.