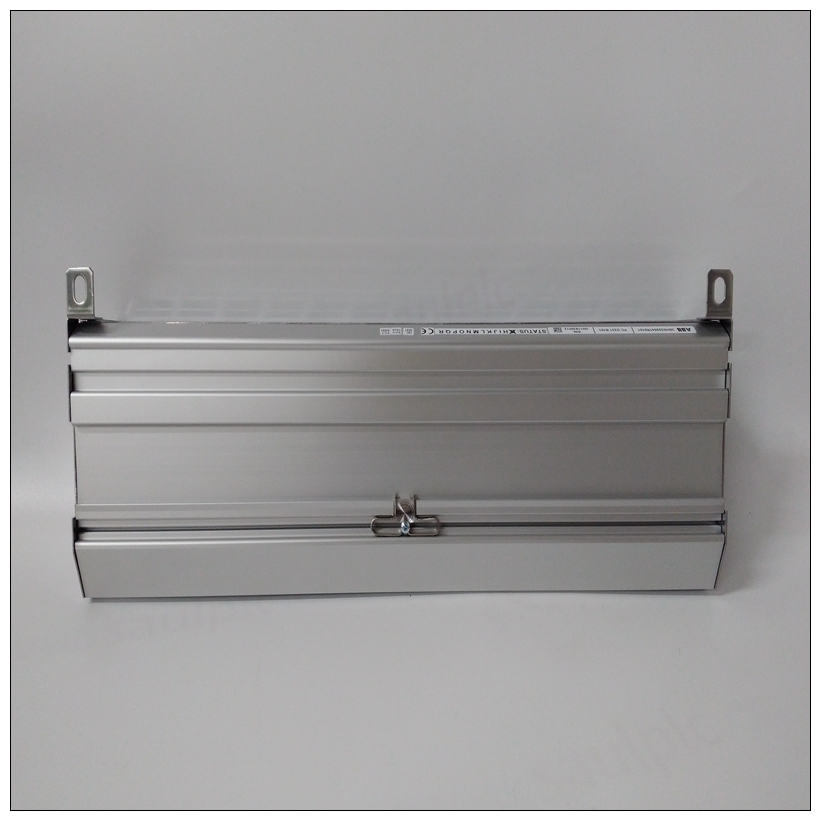

PCD231B101 3BHE025541R0101控制模块,ABB配置手册

MASUAT位允许软件将主机配置为提供UAT数据传输能力。设置MASUAT位到1配置主机以执行未对齐的VMEbus必要时循环。如果位被清除,则MC68030被确认,从而中断未对齐的转换为多个对齐的循环。这一位是由SYSRESET清除。注意,同时使主机提供UAT数据传输能力,VMEbus规范要求所有D32从机都支持它。

PCD231B101 3BHE025541R0101控制模块位4该位由SYSRESET清除。它应该保持畅通。位5设置MASWP位加速MC68030对VMEbus。但是,应谨慎使用。什么时候MASWP(主写过账)设置,MC68030写入周期为VMEchip确认VMEbus,然后再执行实际上已经完成了VMEbus。VMEchip完成写入自行循环,允许MC68030继续有了新的周期。如果SLVEN位被清除(从禁用),则VMEchip甚至在获得之前就确认VME写入VMEbus主控权。如果设置了SLVEN位,则它会等到已获得VMEbus mastership。该位被清除系统重置。注意:如果出现错误,则不会通过BERR*通知MC68030在VMEchip完成写投递时发生周期VMEchip可以编程为中断MC68030,如果发生此类事件(WPERREN位在实用程序中断掩码寄存器)。请记住中断通知可能在事件发生后很长时间内发出错误。位6 020-应始终清除该位。位7 DDTACK-对于25 MHz电路板,应始终清除该位并设置为32 MHz板。必须更改从配置中的位仅当VMEchip控制VMEbus时。更换从机的建议步骤配置为:a、 在请求程序配置中设置DWB位注册到1。b、 读取DHB状态位,直到其为1。c、 更改从配置寄存器。d、 将DWB位清除为0。

The MASUAT bit allows software to configure the master to

provide the UAT data transfer capability. Setting the MASUAT

bit to 1 configures the master to execute unaligned VMEbus

cycles when necessary.

If the bit is cleared, the MC68030 is acknowledged so as to break

the unaligned transfer into multiple aligned cycles. This bit is

cleared by SYSRESET.

Note While making it optional for the master to provide the

UAT data transfer capability, the VMEbus

specification requires that all D32 slaves support it.

Bit 4 This bit is cleared by SYSRESET. It should remain cleared.

Bit 5 Setting the MASWP bit speeds up MC68030 writes to the

VMEbus. However, it should be used with caution. When

MASWP (Master Write Posting) is set, MC68030 write cycles to

the VMEbus are acknowledged by the VMEchip, before they

have actually finished on the VMEbus. The VMEchip finishes

the write cycles on its own, allowing the MC68030 to continue

with new cycles. If the SLVEN bit is cleared (slave disabled), the

VMEchip acknowledges VME writes even before it has obtained

VMEbus mastership. If the SLVEN bit is set, then it waits until it

has obtained VMEbus mastership. This bit is cleared by

SYSRESET.

Note The MC68030 is not notified via BERR* if an error

occurs while the VMEchip is finishing a write posted

cycle. The VMEchip can be programmed to interrupt

the MC68030 if such an event occurs (WPERREN bit in

the Utility Interrupt Mask Register). Keep in mind that

interrupt notification could be well after the occurrence

of the error.

Bit 6 020 - This bit should always be cleared.

Bit 7 DDTACK - This bit should always be cleared for 25 MHz boards

and set for 32 MHz boards. The bits in the slave configuration must be changed

only when the VMEchip has control of the VMEbus.

The recommended procedure for changing the slave

configuration is:

a. Set the DWB bit in the requester configuration

register to 1.

b. Read the DHB status bit until it is 1.

c. Change the slave configuration register.

d. Clear the DWB bit to 0.