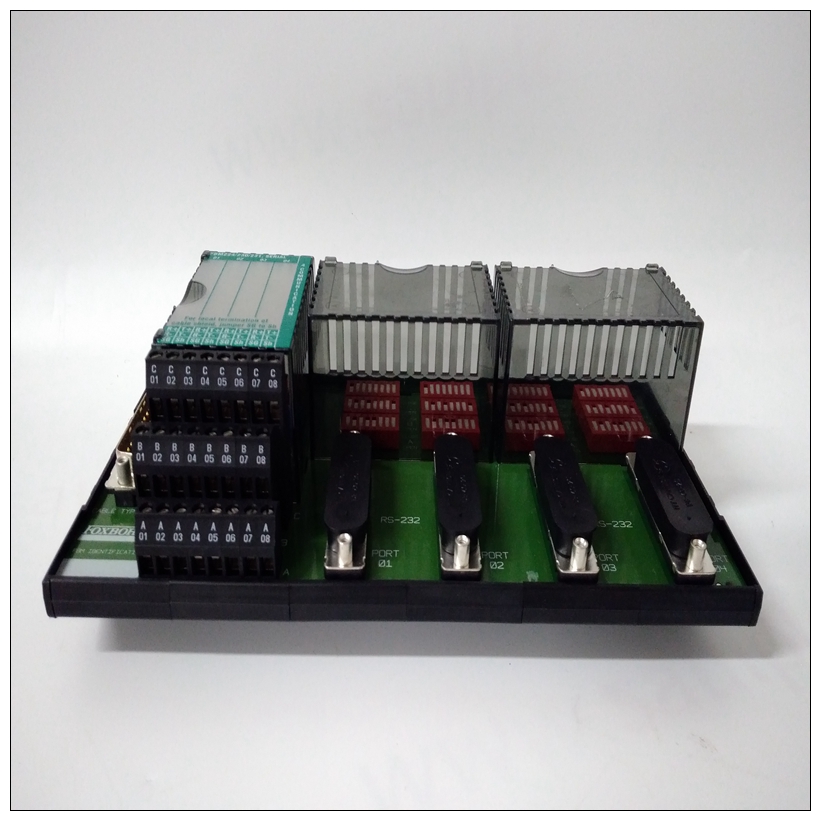

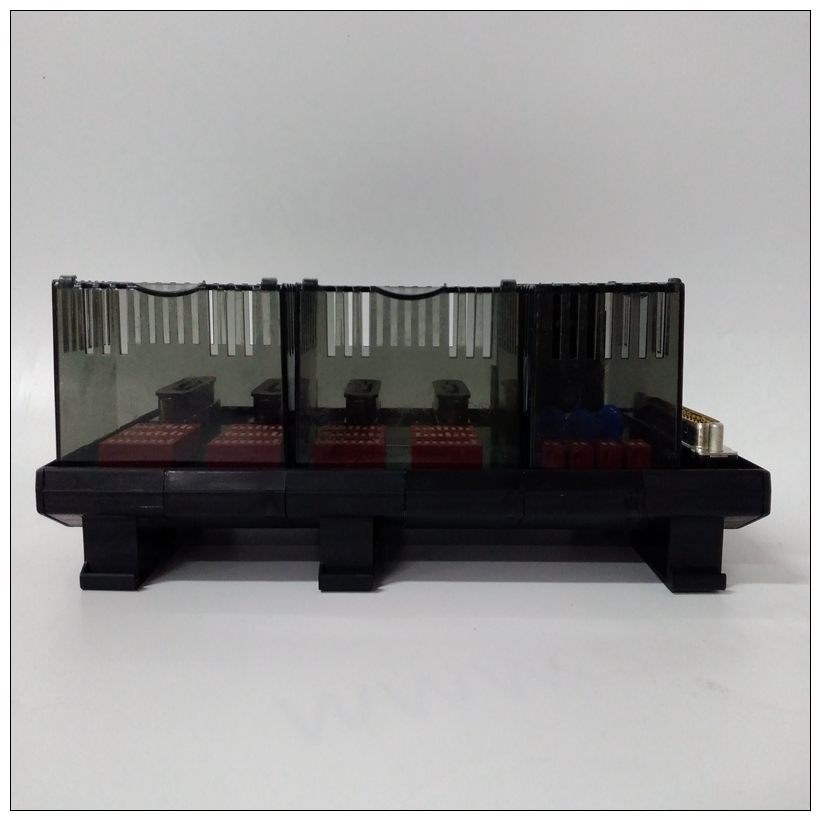

P0926GH冗余总线卡,FOXBORO中文PDF用户手册

SCON状态位反映了收割台J3。连接J3针脚1和2时,启用MVME147充当VMEbus系统控制器,然后是SCON= 1. 当J3针脚1和2未连接时,MVME147为不是VMEbus系统控制器,SCON=0。位1该位允许软件启动全局重置序列。设置SRESET位将激活主机上的SYSRESET*信号VMEbus,反过来重置MVME147。此位清除重置完成后自动执行。该位被清除任何重置。

P0926GH冗余总线卡位2将BRDFAIL设置为1会导致VMEchip尝试激活VMEbus上的SYSFAIL*信号。GCSR位抑制

全局寄存器1中的SYSFAIL(ISF)使MVME147能够由于的状态,导致SYSFAIL*被激活BRDFAIL。此外,当设置位时,故障指示灯点亮。(A)PCC的看门狗超时也会点亮故障指示灯。)

该位由任何重置设置。位3 ROBIN位配置VMEbus仲裁模式。ROBIN=1强制循环模式。ROBIN=0强制优先级模式。MVME147可以使用这两种模式。这位由SYSRESET清除。这些位通过任何重置设置为1,1。注意,写入REQLEV1,0不会更改实际请求者级别,直到MVME147执行以下操作:拥有并释放VMEbus主控权。这意味着有时,写入REQLEV1,0的值不会匹配当前请求者级别(请求级别滞后)。在此期间,REQLEV1,0的读数反映了实际者级别,而不是写入REQLEV1,0的值。位3将该位设置为1可防止请求者释放VMEbus。但是,与DWB控制位不同,设置

RNEVER位不会导致请求者请求VMEbus。清除RNEVER位允许请求者根据其他控制位放弃VMEbus请求者配置寄存器。该位被任何重置。

The SCON status bit is a reflection of the configuration of

header J3. When J3 pins 1 and 2 are connected, enabling the

MVME147 to act as the VMEbus system controller, then SCON

= 1. When J3 pins 1 and 2 are not connected, the MVME147 is

not the VMEbus system controller and SCON = 0.

Bit 1 This bit allows the software to initiate a global reset sequence.

Setting the SRESET bit activates the SYSRESET* signal on the

VMEbus which in turn resets the MVME147. This bit clears

automatically after the reset is complete. This bit is cleared by

any reset.

Bit 2 Setting BRDFAIL to 1 causes the VMEchip to attempt to activate

the SYSFAIL* signal on the VMEbus. The GCSR bit Inhibit

SYSFAIL (ISF), in global register 1, enables the MVME147 to

cause SYSFAIL* to be activated as a result of the state of

BRDFAIL. In addition, when the bit is set, the FAIL LED is lit. (A

watchdog time-out from the PCC also lights the FAIL LED.)

This bit is set by any reset.

Bit 3 The ROBIN bit configures the VMEbus arbitration mode.

ROBIN = 1 forces the round-robin mode. ROBIN = 0 forces the

priority mode. Both modes can be used by the MVME147. This

bit is cleared by SYSRESET. These bits are set to 1, 1 by any reset.

Note that writes to REQLEV1,0 do not change the actual

requester level until the MVME147 goes through the action of

having VMEbus mastership and releasing it. This means that

there are times when the value written into REQLEV1,0 do not

match the current requester level (the request level is lagging).

During such times, reads to REQLEV1,0 reflect the actual

requester level, not the value written into REQLEV1,0.

Bit 3 Setting this bit to 1 prevents the requester from releasing the

VMEbus. However, unlike the DWB control bit, setting the

RNEVER bit does not cause the requester to request the

VMEbus. Clearing the RNEVER bit allows the requester to

relinquish the VMEbus in accordance with the other control bits

of the requester configuration register. This bit is cleared by any

reset.