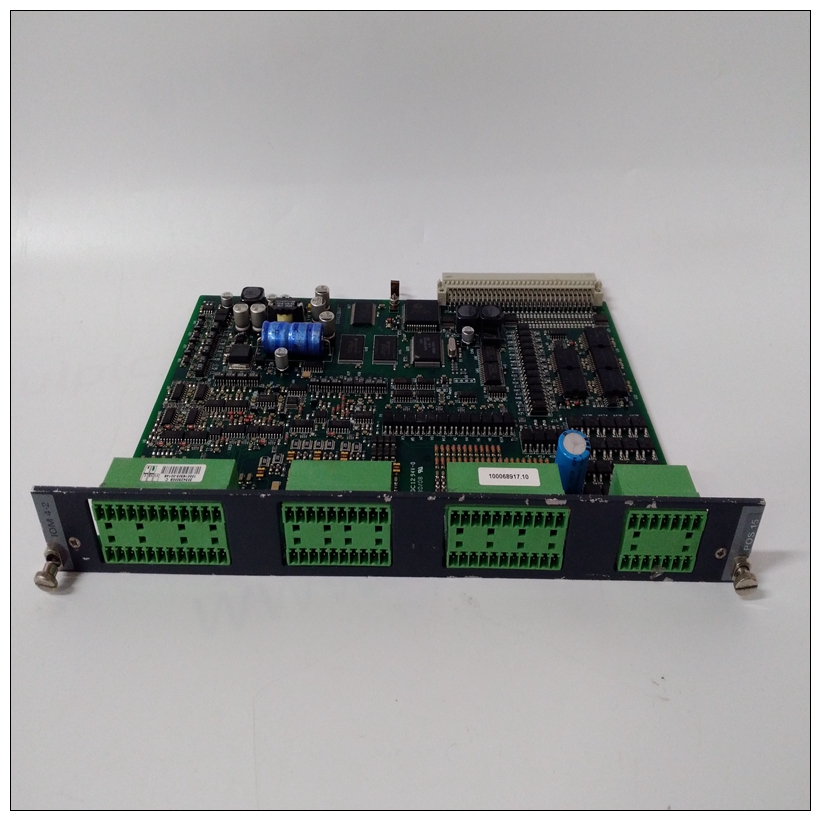

DEIF IOM4.2 2044230041E 2044230040H伺服模块

WAITRMC控制MVME147的多个解决RMC(MARMC)循环。设置WAITRMC时MVME147在执行之前始终等待VMEbus主控MARMC循环。如果需要,则应设置WAITRMC保证MARMC循环的不可分割性(仅当其他主机以与相同的方式实现MARMC循环MVME147)。当WAITRMC被清除时,MVME147仅等待VMEbus如果MARMC循环开始于VMEbus,则为mastership。

DEIF IOM4.2注意,无论WAITRMC位的状态如何,如果MVME147在MARMC,它会一直保持到MARMC已完成。只有当VMEchip中的MASWP位时,WAITRMC操作才有效清除LCSR(位5$FFFE2005)(禁用MASWP过帐。)位6-7这些位确定可访问的本地DRAM部分DMA期间的喷枪。这些位对生成的中断级别进行编程。0级不会生成中断。位3当该位为高位时,中断被启用。中断是此位低时禁用。位7当中断被禁用时,该位为低,为高当中断被启用时。这些位表示PCC的修订级别。初始零件释放为0级。如果需要在在以后的部分中,修订级别将增加。这允许如果功能更改PCC中要求。STAT12表示保险丝+12V电源的状态以太网收发器电源和串口上拉电源。位1低总是0。当打印机忙时,位3 BSY为1,不忙时为0。当打印机处于缺纸状态时,位4 PE为1;当打印机处于缺纸状态时,位4 PE为0事实并非如此。选择打印机时,位5 SELECT为1,未选择打印机时为0。当打印机处于故障状态时,位6故障为1,当打印机处于故障状态时,位6故障为0

不当打印机确认为真时,位7 ACK为1,否则为0。

WAITRMC controls the MVME147 implementation of multiple

address RMC (MARMC) cycles. When WAITRMC is set, the

MVME147 always waits for VMEbus mastership before executing

an MARMC cycle. WAITRMC should be set if it is desired to

guarantee indivisibility of MARMC cycles (only guaranteed if the

other master implements MARMC cycles the same way as the

MVME147).

When WAITRMC is cleared, the MVME147 only waits for VMEbus

mastership if the MARMC cycle starts out by going to the VMEbus.

Note Regardless of the state of the WAITRMC bit, if the

MVME147 obtains VMEbus mastership during an

MARMC, it maintains it until all of the cycles of

the MARMC are completed.

WAITRMC operation is effective only if MASWP bit in the VMEchip

LCSR (bit 5 $FFFE2005) is cleared (MASWP posting is disabled.)

Bits 6-7 These bits determine the section of local DRAM that is accessible to

the LANCE during DMA. These bits program the interrupt level that is generated. Level 0

does not generate an interrupt.

Bit 3 When this bit is high, the interrupt is enabled. The interrupt is

disabled when this bit is low.

Bit 7 This bit is low when the interrupt is disabled and it is high

when the interrupt is enabled.These bits represent the revision level of the PCC. Initial parts

are released as level 0. If functional changes are required in

future parts, the revision level is incremented. This allows the

software to configure itself should functional changes be

required in the PCC. STAT12 indicates the status of the fused +12V power for

Ethernet transceiver power and for serial port pull up power.

Bit 1 LOW is always 0.

Bit 3 BSY is 1 when the printer is busy and 0 when it is not.

Bit 4 PE is 1 when the printer is in the paper empty state and 0 when

it is not.

Bit 5 SELECT is 1 when the printer is selected and 0 when it is not.

Bit 6 FAULT is 1 when the printer is in the fault state and 0 when it is

not.