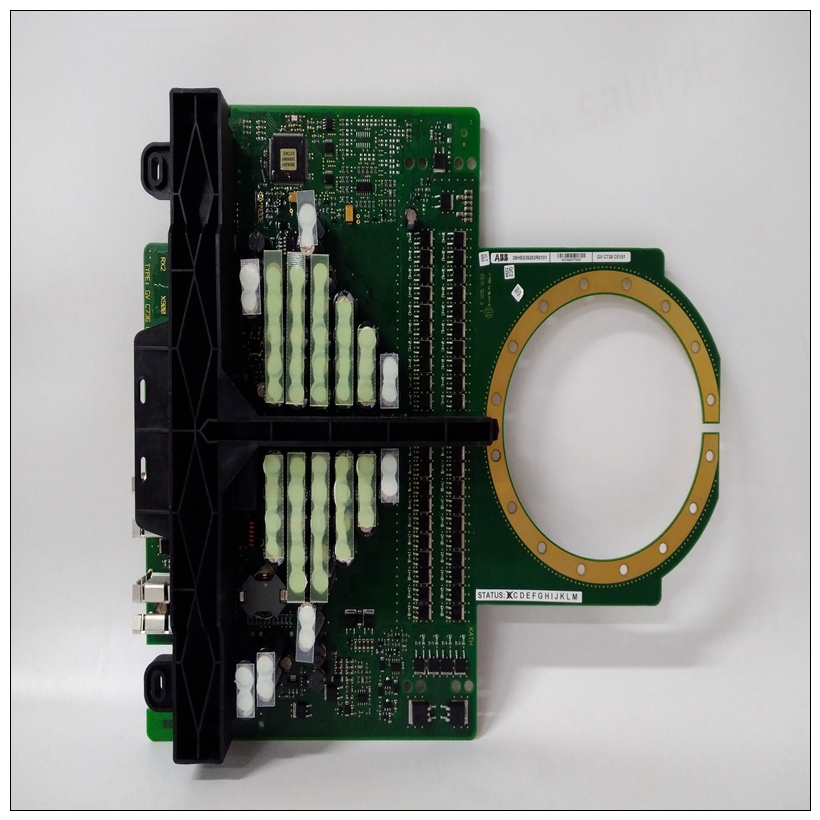

GVC736CE101 3BHE039203R0101 5SXE12-0184模块,中文PDF使用手册

这些位编程串行端口的中断级别生成级别0不生成中断。位3当该位为高位时,中断被启用。中断是此位低时禁用。位4该位控制矢量源。当该位较低时中断状态/id矢量来自串行芯片。当这个位高,中断状态/id向量来自PCC。位7当该位为高位时,产生串行端口中断在位0-2中编程的电平。该位是电平敏感的当中断启用和串行端口中断时,它处于活动状态处于活动状态。这些位控制本地RAM奇偶校验。

GVC736CE101 3BHE039203R0101 5SXE12-0184模块这些位应该未在MVME147-010上启用。这些位通过重置。MVME147上的DRAM奇偶校验处于未定义状态通电后的状态。读取未初始化内存启用奇偶校验会导致总线错误。全部的应写入DRAM位置以确保正确启用检查前奇偶校验。0本地RAM奇偶校验已禁用。1启用本地RAM奇偶校验,并断言BERR在当前DRAM访问周期期间(添加1个等待周期)。2本地RAM奇偶校验被禁用。3启用本地DRAM奇偶校验。BERR被断言在LANCE、VME的当前周期(添加1个等待周期)上,PCC访问DRAM。BERR在下一个MC68030访问DRAM的DRAM访问周期(增加0等待周期)。注意,BERR不仅在下一个MC68030 DRAM访问周期,但在所有后续MC68030 DRAM访问周期。这很有帮助当DRAM坏时,停止MC68030继续。该位用于测试奇偶校验生成和检查逻辑。当该位较低时,将正确的奇偶校验写入DRAM;当奇偶校验为高时,将不正确的奇偶校验写入DRAM。这一位是通过重置清除。位3设置时,该位用于启用本地总线计时器,即PCC的一部分。因为VMEchip还包含一个本地总线定时器,应清除该位,关闭PCC本地总线计时器。该位通过重置清除。位4该位为主中断启用。当该位较低时,所有MVME147上的中断被禁用;高时,所有中断已启用。该位通过重置清除。位5-7当模式%101写入这些位时,前面板重置开关被禁用。复位开关可用于任何其他模式。这些位通过重置清除。

These bits program the interrupt level that the serial ports

generate. Level 0 does not generate an interrupt.

Bit 3 When this bit is high, the interrupt is enabled. The interrupt is

disabled when this bit is low.

Bit 4 This bit controls the vector source. When this bit is low, the

interrupt status/id vector comes from the serial chip. When this

bit is high, the interrupt status/id vector comes from the PCC.

Bit 7 When this bit is high, a serial port interrupt is being generated

at the level programmed in bits 0-2. This bit is level sensitive

and it is active when interrupt enable and serial port interrupt

are active.These bits control local RAM parity checking. These bits should

not be enabled on the MVME147-010. These bits are cleared by

reset. The DRAM parity on the MVME147 is in an undefined

state after power-up. Reads to uninitialized memory

with parity checking enabled causes bus errors. All

DRAM locations should be written to ensure correct

parity before checking is enabled.

0 Local RAM parity checking is disabled.

1 Local RAM parity checking is enabled and BERR is asserted

during the current DRAM access cycle (adds 1 wait cycle).

2 Local RAM parity checking is disabled.

3 Local DRAM parity checking is enabled. BERR is asserted

on the current cycle (adds 1 wait cycle) for LANCE, VME,

and PCC accesses to DRAM. BERR is asserted on the next

DRAM access cycle for MC68030 accesses to DRAM (adds 0

wait cycles). Note that not only is BERR asserted during the

next MC68030 DRAM access cycle but it is asserted during

all subsequent MC68030 DRAM access cycles. This helps

stop the MC68030 from proceeding when DRAM is bad.This bit is used to test the parity generating and checking logic.

When this bit is low, correct parity is written to the DRAM;

when high, incorrect parity is written to the DRAM. This bit is

cleared by reset.

Bit 3 When set, this bit is used to enable the local bus timer that is

part of the PCC. Because the VMEchip also contains a local bus

timer, this bit should be cleared, turning off the PCC local bus

timer. This bit is cleared by reset.

Bit 4 This bit is the master interrupt enable. When this bit is low, all

interrupts on the MVME147 are disabled; when high, all

interrupts are enabled. This bit is cleared by reset.