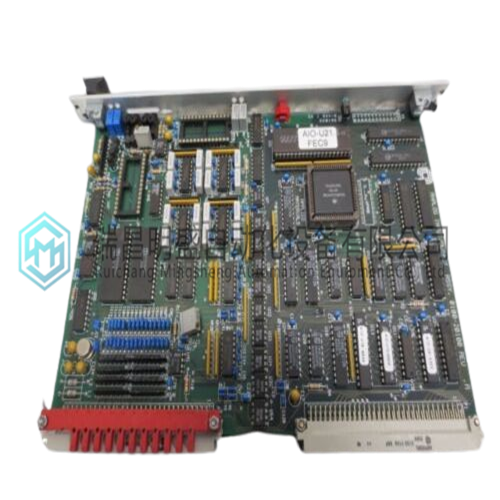

AMAT 0100-20100 VME I/O 板

1.产 品 资 料 介 绍:

中文资料:

AMAT 0100-20100字节排序:大字节/小字节由于主要微处理器制造商摩托罗拉和英特尔的传统不同,字节排序问题存在。VMEbus板是围绕摩托罗拉的680X0处理器和兼容性设计的,这些处理器和兼容性将多个字节值存储在内存中,最高有效字节位于最低字节地址。这种字节排序方案被称为“Big Endian”排序。另一方面,英特尔的80X86微处理器在内存中存储多个字节值,其中最低有效字节位于最低字节地址,因此得名“Little Endian”排序

AMAT 0100-20100的PCI到VMEbus接口使用基于英特尔或等效的桥接芯片,该芯片使用Little Endian字节排序。字节排列以及处理器中的数据与存储器中传输的数据之间的字节关系如图1-2所示。

请注意,在Little Endian设备中,在多字节写入(如所示的L字传输)后,内存的最低有效字节存储在最低字节地址中,而反射内存的最高有效字节则存储在此类传输后的最高字节地址中AMAT 0100-20100

英文资料:

Byte Ordering: Big Endian / Little Endian The byte-ordering issue exists due to the different traditions at the major microprocessor manufacturers, Motorola and Intel. VMEbus boards are designed around Motorola’s 680X0 processors and compatibles, which store multiple-byte values in memory with the most significant byte at the lowest byte address. This byte-ordering scheme became known as “Big Endian” ordering. On the other hand, Intel’s 80X86 microprocessors, store multiple-byte values in memory with the least significant byte in the lowest byte address, earning the name “Little Endian” ordering

The AMAT 0100-20100’s PCI-to-VMEbus interface uses an Intel based or equivalent bridge chip, which uses Little Endian byte ordering. Byte arrangement and the byte relationship between data in the processor and transferred data in memory are shown in Figure 1-2.AMAT 0100-20100

Note that in Little Endian devices, the Memory’s least significant byte is stored in the lowest byte address after a multiple-byte write (such as the Lword transfer illustrated), while the Reflective Memory’s most significant byte is stored in the highest byte address after such transfersAMAT 0100-20100

2.产 品 展 示

3.主 营 品 牌

本篇文章出自瑞昌明盛自动化设备有限公司官网,转载请附上此链接:http://www.jiangxidcs.com