主营产品

PLC可编程控制器模块,DCS卡件,ESD系统卡件,振动监测系统卡件,汽轮机控制系统模块,燃气发电机备件等,优势品牌:Allen Bradley、BentlyNevada、ABB、Emerson Ovation、Honeywell DCS、Rockwell ICS Triplex、FOXBORO、Schneider PLC、GE Fanuc、Motorola、HIMA、TRICONEX、Prosoft等各种进口工业零部件

产品广泛应用于冶金、石油天然气、玻璃制造业、铝业、石油化工、煤矿、造纸印刷、纺织印染、机械、电子制造、汽车制造、塑胶机械、电力、水利、水处理/环保、锅炉供暖、能源、输配电等等

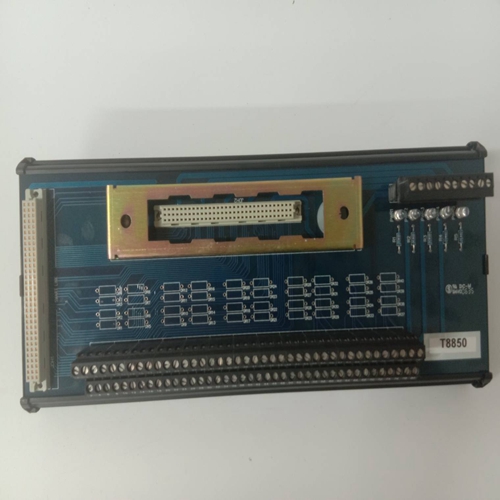

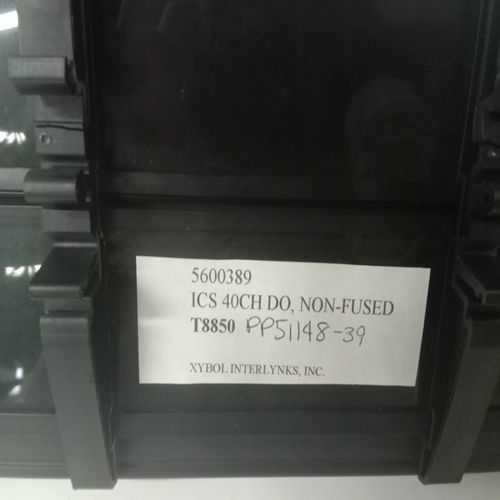

ICS T8850处理器卡件

主延迟用于延迟来自跟随器重合闸功能的闭合命令的信号的I/P。

该信号在主重合闸功能的死区时间开始时出现,并在循环的最后一次重合闸,或在主控成功重合闸后等待时间结束时。如果不需要,则设置为“off”(“F”或“False”)。

Mast.noSucc来自主CB的阻塞信号的I/P。

该信号由“Def.Trip”上升沿触发主重合闸功能的输出,并在500毫秒的固定时间。

如果不需要,则设置为“off”(“F”或“False”)。延迟FLWR。

只要主断路器尚未完成其自动重合闸循环,就发出信号延迟跟随器CB。

信号在主AR死区时间开始时拾取,并且由“Def”的上升沿重置。跳闸输出或“关闭CB”输出在时间“tClose”后的下降沿。Blk.toFlwr

只要主CB不成功。

该信号的偏移与“Def.Trip”相同

输出双重逻辑

CB2就绪当CB2准备就绪时,由CB2信号激励的I/P(打开/关闭/打开)。

如果不需要或未安装,则设置为“关闭”(“F”或“假”)。

I/P逻辑:“CB就绪”或“CB2就绪”在双工方案中,自动重合闸循环由激活的“CB就绪”或“CB2就绪”I/P启用。该输入的复位在内部延迟100ms。

CO就绪2当CB2准备就绪时,由CB2信号激励的I/P关闭/打开操作。

设置为“开”(“T”或“真”),如果不需要,则不安装和“死”不使用第2行。

用于启用关闭命令的I/P逻辑:[(“同步检查2”)和“CO就绪2”)或“死线2”或“ExtSCBypas”]。

CB2公开赛当CB2打开时,由来自CB2的信号激励的I/P。

如果不需要,则设置为“on”(“T”或“True”)。观察在双工方案中为双工逻辑提供的信息

MasterDelay

I/P for a signal delaying the closing command from the follower reclosure function.

This signal picks up when the dead time of the master reclosure function starts and is reset either by a new trip after the

last reclosure of the cycle or at the end of the wait time following successful reclosure by the master.

Set to ‘off’ (‘F’ or ‘False’), if not needed.

Mast.noSucc

I/P for a blocking signal from the master CB.

This signal is triggered by the rising edge of the ‘Def.Trip’

output from the master reclosure function and resets after a

fixed time of 500 ms.

Set to ‘off’ (‘F’ or ‘False’), if not needed.

DelayFlwr.

Signal to delay the follower CB for as long as the master circuit-breaker has not completed its auto-reclosure cycle.

The signal picks up at the start of master AR dead time and

is reset either by the rising edge of the ‘Def.Trip’ output or the

falling edge of the ‘Close CB’ output after the time ‘tClose’.

Blk.toFlwr

Signal to block the follower CB as long as reclosure of the

master CB is unsuccessful.

The excursion of this signal is the same as for the ‘Def.Trip’

output.DUPLEX LOGIC

CB2 Ready

I/P excited by a signal from CB2 when it is ready

(open/close/open).

Set to ‘off’ (‘F’ or ‘False’), if not needed or not fitted.

I/P logic: ‘CB ready’ OR ‘CB2 ready'

In a duplex scheme, the auto-reclosure cycle is enabled either by an active ‘CB ready’ or ‘CB2 ready’ I/P.

Resetting of this input is delayed internally by 100 ms.

CO Ready 2

I/P excited by a signal from CB2 when it is ready for a

close/open operation.

Set to ‘on’ (‘T’ or ‘True’), if not needed, not fitted and ‘Dead

line 2’ is not used.

I/P logic for enabling the close command:: [(‘synchrocheck2’

AND ‘CO Ready 2’) OR ‘Dead line 2’ OR ‘ExtSCBypas'].

CB2 open

I/P excited by a signal from CB2 when it is open.

Set to ‘on’ (‘T’ or ‘True’), if not needed. Observe the information given for the duplex logic in a duplex scheme