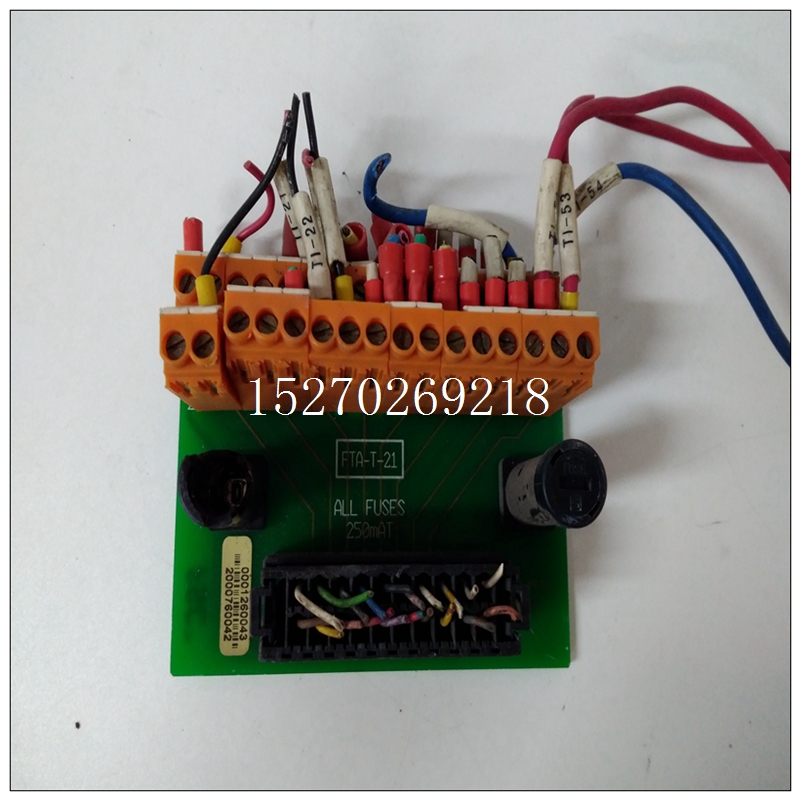

HONEYWELL FTA-T-21使用参数,FTA-T-21卡件

三组VMEbus信号控制与电路板的通信。具体如下:a、 数据总线D00至D15

b、 地址行A01、A02、A03、A04、A05、A06、A07c、 总线控制信号:

(1) 写入(2) DS0,*DS1*(3) 系统时钟(4) 系统重置*

数据总线是双向的,可以在电路板之间移动数据通过16位数据收发器响应来自控制的控制信号解码器。数据收发器用作内部数据总线的缓冲器,该总线互连板上的所有数据设备。

HONEYWELL FTA-T-21使用参数地址线A01到A07映射128个通信寄存器在VME地址空间内的256字节范围内(第4节)。控制信号确定数据是移动到VMIVME-3112(写入)还是从VMIVME-3112(读取)提供必要的数据选通(DS0、DS1)和提供16 MHz时钟(SYS CLK),供车载计时器使用。系统复位输入重置所有计时器和标志。静态控件锁存在控制寄存器中并使用主要是建立董事会的运作模式。必要的状态标志用于监测和控制模拟输入多路复用器和ADC通过状态寄存器。参考控制和状态寄存器统称为控制和状态寄存器(CSR),因为它们位于同一位置住址写入信号决定访问哪一个。大部分控件可以通过状态寄存器直接监控寄存器输出。3.4模数转换器(ADC)控制和定时与控制ADC相关的控制命令和状态标志如图3.3-1所示,并在第4节和以下章节中进行了描述。CSR中有三个模式控制位。这些程序的编程控制位(模式0H到模式2H)确定五个ADC中的哪一个电路板操作模式。五种ADC工作模式和控制寄存器模式控制位是ADC操作模式,基本上决定了板载ADC和通道选择由CPU板或板载外部控制通道定序器。它们还确定是否将生成中断转换完成时。五种ADC操作模式为第4节从编程的角度进行了描述。自动扫描模式(模式0)、随机轮询模式和这里将讨论扫描轮询模式,以揭示ADC控制和定时间隔。其他两种模式使用中断而不是轮询来确定当一个转换或一系列转换完成时

After board-selection has occurred, three groups of VMEbus signals

control communications with the board. They are as follows:

a. Data Bus lines D00 to D15

b. Address lines A01, A02, A03, A04, A05, A06, A07

c. Bus Control Signals:

(1) WRITE

(2) DS0,* DS1*

(3) SYS CLK

(4) SYS RESET*

Data bus lines are bi-directional and move data to and from the board

through a 16-bit data transceiver in response to control signals from the control

decoder. The data transceiver serves as a buffer for the internal data bus which

interconnects all data devices on the board.

Address lines A01 through A07 map the 128 communication registers

onto a 256-byte range within the VME address space (Section 4). The control

signals determine whether data is to be moved to the VMIVME-3112 (write) or from

the VMIVME-3112 (read), provide the necessary data strobes (DS0, DS1), and

supply a 16 MHz clock (SYS CLK) for use by on-board timers. A SYS RESET input

resets all timers and flags.

Static controls are latched into the Control Register and are used

primarily to establish the operational mode of the board. Status flags, necessary

for monitoring and controlling the analog input multiplexer and the ADC are read

through the Status Register. The control and status registers are referred to

collectively as the Control and Status Register (CSR), since they are at the same

address. The WRITE signal determines which one is accessed. Most of the control

register outputs can be monitored directly through the Status Register.

3.4 ANALOG-TO-DIGITAL (ADC) CONTROL AND TIMING

Control commands and status flags associated with controlling the ADC

are illustrated in Figure 3.3-1, and are described in Section 4 and the following sections.

There are three mode control bits in the CSR. The programming of these

control bits (Mode 0H through Mode 2H) determine which one of five ADC

operating modes the board is to operate in. The five ADC operating modes and the

Control Register mode control bits areThe ADC operating modes basically determine if the on-board ADC and

channel selection are controlled externally by a CPU board or by the on-board

channel sequencer. They also determine whether an interrupt will be generated

when the conversion(s) are complete. The five ADC operating modes will be

described from a programming viewpoint in Section 4.

The AUTO SCANNING MODE (Mode 0), RANDOM POLL MODES, and

SCANNING POLL MODE will be discussed here to reveal the ADC controls and

timing intervals. The other two modes use interrupts instead of polling to determine

when a conversion or a series of conversions are completed.